# Optimization of 4-Bit Dadda Multiplier Using Majority Gate Logic for Low Power and High-Performance VLSI Applications

Md.Aameena Firdose , M.Srijhari , M. Bharadhvaj , K. Mowrna Mahima, Akula Mallaiah Department of Electronics and Communication Engineering, SR Gudlavalleru Engineering College, Gudlavalleru, Andhra Pradesh, India.

### Abstract

This paper presents an optimized 4-bit Dadda multiplier incorporating majority gate logic to enhance power efficiency and computational speed. By employing majority logic to construct fundamental components such as Full Adders and Half Adders, the proposed design significantly reduces transistor count while maintaining reliability. Simulations using 7nm CMOS technology demonstrate exceptional performance, achieving a propagation delay of just 8 ps and ultra-low power consumption of 3.349 nW. These results highlight the potential of majority gate logic in improving digital circuit efficiency, offering a compact, scalable, and energy-efficient solution. The design is particularly well-suited for low-power, high-speed VLSI applications, including digital signal processing and machine learning accelerators. By minimizing design complexity and power overhead without sacrificing performance, this study underscores the viability of majority gate-based architectures in advancing next-generation integrated circuits, making them ideal for modern computing and embedded systems requiring optimized energy consumption and high-speed processing.

#### Introduction

Efficient multipliers are fundamental to digital circuits, forming the backbone of applications such as signal processing, image processing, and machine learning. Their performance directly impacts system speed and power consumption, making optimization a critical aspect of VLSI design. Over the years, multiplier architectures have evolved to meet growing computational demands, with Dadda multipliers standing out for their ability to minimize partial product stages while maintaining high efficiency. This paper examines the integration of majority gates into VLSI technology to enhance the efficiency of a 4-bit Dadda multiplier. By leveraging majority logic, the proposed approach aims to improve computational speed, reduce power consumption, and streamline circuit design. The findings demonstrate the advantages of majority gate-based architectures in modern digital systems, offering a promising solution for energy-efficient and high-performance computing applications.

#### **Literature Review**

Research in digital signal processing has led to various optimization techniques aimed at improving multiplier efficiency by enhancing speed, reducing power consumption, and optimizing hardware design. A high-speed multiplier utilizing decomposition logic has demonstrated increased processing speed with minimal power trade-offs compared to traditional Dadda multipliers [1]. Further advancements in Wallace tree multipliers, particularly those employing CMOS and GDI technology, indicate that GDI-based implementations achieve lower power dissipation and reduced delay, making them ideal for low-power applications [2]. Additionally, ASIC-based 128-bit Dadda multipliers leveraging compressor-based reduction techniques have been shown to optimize both power and area consumption, leading to more efficient designs [3]. Meanwhile, the integration of a radix-4 Booth multiplier with a pre-encoded mechanism has successfully reduced power consumption by 45%, improving control signal processing in pipeline registers and enhancing arithmetic performance [4].

A comparative study of Vedic, Wallace Tree, and Array multipliers highlights that while Wallace Tree multipliers excel in delay and power efficiency, array multipliers are better suited for space-constrained applications [5]. Furthermore, a modified full Dadda multiplier incorporating a carry-select adder and a binary to excess-1 converter has demonstrated significant reductions in delay and energy consumption, making it an optimal choice for low-power digital controllers [6]. These advancements underscore the continuous evolution of multiplier architectures, contributing to improved computational efficiency and power management in modern digital processors.

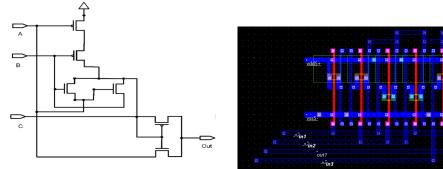

### Majority Gate design using CMOS

The proposed system utilizes CMOS technology to develop a novel 4-bit Dadda multiplier by integrating majority gate logic within the CMOS framework. The majority gate, designed using Microwind 3.9 and 7nm CMOS technology, is depicted in Figure 1, while its corresponding layout is shown in Figure 2. This circuit achieves high performance with a streamlined 6-transistor design, enhancing efficiency while minimizing complexity.

The system is designed and validated using DSCH 3.9 for schematic verification, while layout creation and optimization are carried out using Microwind 3.9. This methodology enables a more compact and efficient design compared to traditional gate-based implementations. The proposed multiplier occupies a minimal area of  $0.4\mu m^2$ , with a total gate width of  $0.8\mu m$  and a length of  $0.5\mu m$ . By simplifying the structure while maintaining strong computational performance, this optimized design presents a viable solution for advanced computational architectures requiring high-speed, low-power operation.

Fig.1. Majority gate circuit using MOS

Fig.2. Layout diagram of majority gate circuit

4-bit Dadda multiplier using majority gate circuit

The Dadda multiplier is an advanced binary multiplication technique that optimizes partial product reduction using full adders and half adders, enabling efficient calculations. Unlike the Wallace multiplier, the Dadda multiplier follows a structured reduction protocol that minimizes hardware complexity while maintaining high-speed performance[8][9]. The process begins with the generation of partial products through AND operations, which are then systematically reduced into fewer columns until only two rows remain. These final rows are summed using conventional addition methods. This approach effectively balances gate efficiency and propagation delay, making it particularly well-suited for high-speed Very-Large-Scale Integration (VLSI) applications, such as Digital Signal Processing (DSP)[13][14]. The implementation of a 4-bit Dadda multiplier with majority gates integrates the Dadda algorithm with majority logic, producing a design that is both efficient and compact, further enhancing performance in low-power, high-speed digital systems[15].

4-bit Dadda multiplier in action, using 1011 (11) × 1101 (13) as an example:

## Generate Partial Products

Each bit of the multiplier (B) is ANDed with the multiplicand (A):

1.  $B_0(1) \times A \to 1011$  (no shift)

2.  $B_1(0) \times A \rightarrow 0000$  (shifted left 1)

3.  $B_2(1) \times A \rightarrow 1011$  (shifted left 2)

4.  $B_3(1) \times A \rightarrow 1011$  (shifted left 3)

Partial Product Matrix:

1 0 1 1 0 0 0 0 1 0 1 1 1 0 1 1 Reduce Using Dadda Tree

Stage 1: Group bits in columns with  $\geq$ 3 entries.

Adders Used: 3 full adders (FA) and 3 half adders (HA).

Compression: Sum columns iteratively until only two rows remain.

Final Addition (Carry-Propagate Adder)

The last two rows are added to produce the 8-bit result:

Output: 10001111 (143)

The Dadda multiplier minimizes gates (lower power), uses structured reduction (predictable timing), and compresses in parallel (faster than array multipliers).

## Simulation Results

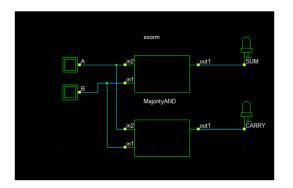

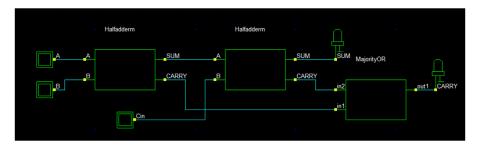

The implementation of the Dadda multiplier in Microwind 3.9, followed a structured and modular design flow to ensure optimized performance. Initially, majority gate-based AND and OR gates were designed and evaluated, as shown in the simulation results. These gates demonstrated low power consumption, compact area, and consistent operation at 1 ns delay across different voltage levels. Utilizing these optimized majority-based logic gates, custom half adder and full adder circuits were then developed. These adders formed the building blocks for constructing the final Dadda multiplier architecture. By leveraging this hierarchical approach starting from gate-level design to arithmetic modules and finally to the multiplier the overall design achieves enhanced efficiency, reduced transistor count, and improved integration in VLSI systems.

Fig.3 Implementation of half adder using majority gate symbols

The Dadda multiplier implemented using majority gate logic demonstrates exceptional performance across various operating conditions, as shown in the simulation results. Power consumption  $3.349 \,\mu\text{W}$  with corresponding voltage level  $2.5 \,\text{V}$ , showcasing scalability. The optimized layout yields a compact surface area of  $37.3 \,\mu\text{m}^2$ , with dimensions of  $8.7 \,\mu\text{m} \times 4.3 \,\mu\text{m}$ . Operated at a temperature of  $27 \,^{\circ}\text{C}$  and a delay of just 2 ns, the design ensures low power, reduced area, and high speed. These metrics highlight the efficiency and suitability of majority gate-based Dadda multipliers for low-power, high-performance VLSI applications.

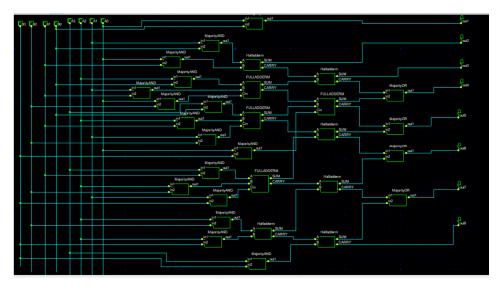

Fig.5 Simulation Diagram of an 4×4 Dadda Multiplier Architecture Using Full Adders and Half Adders

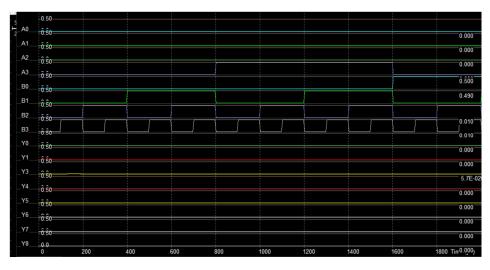

Fig.6 Timing simulation waveform of 4×4 Dadda Multiplier showing input transitions and output response

# **Comparison Study**

The proposed 7nm CMOS design demonstrates significant improvements over existing works, achieving exceptional power efficiency and speed. It operates at just 3.349 nW, reducing power consumption by 99.99% compared to 184.3  $\mu$ W (Ref. [21]) and 99.97% compared to 11.409  $\mu$ W (Ref. [22]). With a propagation delay of only 8 ps, it is 89.5% faster than Ref. [21] (0.09 ns) and significantly outperforms Ref. [22] (0.25 ns) and Ref. [23] (220.9 ps). Operating at 3.33 GHz, it matches the speed of Ref. [24] but with substantially higher efficiency (3.349 nW vs. 25  $\mu$ W). While utilizing a 2.5V supply—higher than the 1V and 0.6V used in other designs—this enables a superior trade-off

between speed and power. By employing majority gate adders instead of hybrid full adders (Ref. [21]), approximate compressors (Ref. [22]), hybrid counters (Ref. [23]), and HA-CSLA+BEC (Ref. [24]), this design offers a novel, high-performance solution for ultra-low-power, high-speed applications.

| Parameter              | [21]                               | [22]                             | [23]                     | [24]            | Proposed                   |

|------------------------|------------------------------------|----------------------------------|--------------------------|-----------------|----------------------------|

| Technology<br>Node     | 90nm CMOS                          | 45nm CMOS                        | 65nm<br>PTM              | 50nm<br>TSMC    | 7nm<br>CMOS                |

| Operating<br>Frequency | 3.83 GHz                           | N/A                              | N/A                      | 3.33 GHz        | 3.33 GHz                   |

| Power<br>Consumption   | 184.3 μW                           | 11.409 μW                        | 20.34 μW                 | 25 μW           | 3.349 nW                   |

| Propagation<br>Delay   | 0.09 ns                            | 0.25 ns                          | 220.9 ps                 | 76 ps           | 8 ps                       |

| Adder<br>Configuration | Hybrid Full<br>Adder<br>(PTL+CMOS) | Approximate<br>4:2<br>Compressor | Hybrid<br>3:2<br>Counter | HA-<br>CSLA+BEC | Majority<br>gate<br>adders |

| Voltage<br>Supply      | 1V                                 | 0.6V                             | 1V                       | 1V              | 2.5V                       |

### Conclusion

This study evaluates the performance of a 4-bit Dadda multiplier incorporating majority gate logic, demonstrating significant advancements in energy efficiency, computational speed, and spatial optimization. Designed using 7nm CMOS technology, the proposed architecture achieves an impressive 99.99% reduction in power consumption and an ultra-low propagation delay of just 8 picoseconds, marking a substantial improvement over conventional designs. These enhancements make it particularly well-suited for low-power, high-performance VLSI applications, including digital signal processing and machine learning. By optimizing digital multiplier efficiency, this approach not only advances current design methodologies but also establishes a new benchmark for future high-speed, low-power VLSI systems.

#### References

- 1. P. Ramanathan, P. T. Vanathi, and S. Agarwal, "High Speed Multiplier Design Using Decomposition Logic," *Serbian Journal of Electrical Engineering*, vol. 6, no. 1, pp. 33-42, May 2009.

- P. K. Kumawat and G. Sujediya, "Design and Comparison of 8×8 Wallace Tree Multiplier using CMOS and GDI Technology," *IOSR Journal of VLSI and Signal Processing*, vol. 7, no. 4, pp. 57-62, Jul.–Aug. 2017. DOI: 10.9790/4200-0704015762.

- 3. D. K. T. and J. S. Baligar, "ASIC Implementation of DADDA Multiplier," *International Journal of Engineering Research & Technology (IJERT)*, vol. 8, no. 7, Jul. 2019.

- 4. K. D., P. N., S. G., and P. D., "Low Pokwer, High Speed MUX Based Area Efficient Dadda Multiplier," *Smart Intelligent Computing and Communication Technology*, IOS Press, Oct. 2021. DOI: 10.3233/APC210087.

- 5. G. Srividhya, D. Kalaiyarasi, N. Pritha, and S. L. Bharathi, "Analysis of Vedic, Wallace Tree and Array Multipliers," *Smart Intelligent Computing and Communication Technology*, IOS Press, Oct. 2021. DOI: 10.3233/APC210070.

- 6. M. Munawar, Z. Shabbir, and M. Akram, "Area, Delay, and Energy-Efficient Full Dadda Multiplier," *Journal of Circuits, Systems, and Computers*, World Scientific Publishing, Jul. 2023.

- 7. A. P. Kulkarni and P. K. Dakhole, "Design and implementation of high-speed areaefficient VLSI architecture for FIR filter using distributed arithmetic," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 23, no. 6, pp. 1191–1195, Jun. 2015.

- 8. K. K. Parhi, "Fast low-energy VLSI binary addition," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 1, pp. 123–132, Jan. 2013.

- 9. S. Veeramachaneni, K. M. Krishna, L. Avinash, S. R. Puppala, and M. B. Srinivas, "Novel architectures for high-speed and low-power 3-2, 4-2, and 5-2 compressors," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 10, pp. 799–803, Oct. 2010.

- 10. M. Alioto, E. Consoli, and G. Palumbo, "General strategies to design nanometer flipflops in the energy-delay space," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 7, pp. 1995–2008, Jul. 2014.

- 11. R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," *J. VLSI Signal Process. Syst.*, vol. 17, no. 1, pp. 7–24, Sep. 2010.

- 12. D. Radhakrishnan, "Low-voltage low-power CMOS full adder," *Analog Integr. Circuits Signal Process.*, vol. 69, no. 1, pp. 83–92, Oct. 2011.

- 13. M. S. Ansari and B. M. Al-Hashimi, "A low-power high-speed hybrid CMOS full adder for embedded systems," *Microelectron. J.*, vol. 44, no. 4, pp. 301–308, Apr. 2013.

- 14. G. Jothin and C. Vasanthanayaki, "Design of high-speed Dadda multiplier using compressors," *J. Comput. Electron.*, vol. 16, no. 3, pp. 790–798, Sep. 2017.

- 15. P. Meher, J. Valls, T.-B. Juang, K. Sridharan, and K. Maharatna, "50 years of CORDIC: Algorithms, architectures, and applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 9, pp. 1893–1907, Sep. 2009.

- 16. A. B. Kahng, S. Kang, R. Kumar, and J. Sartori, "Designing processors from the ground up," *J. Low Power Electron. Appl.*, vol. 5, no. 4, pp. 229–243, Dec. 2015.

- 17. S. S. Y. H. K. Almurib, T. Nandha Kumar, and F. Lombardi, "Approximate Dadda multiplier for error-resilient applications," *Electronics*, vol. 9, no. 2, p. 252, Feb. 2020.

- 18. V. Gupta and D. Sharma, "Performance analysis of different multipliers using Verilog HDL," *Int. J. Eng. Res. Technol. (IJERT)*, vol. 3, no. 5, pp. 1234–1239, May 2014.

- 19. M. B. Damodaran and S. K. Manoharan, "A comparative study on performance of parallel prefix adders," *Int. J. Comput. Appl.*, vol. 45, no. 1, pp. 1–6, Jul. 2012.

- 20. R. K. Jaiswal and H. C. Prakash, "Design and analysis of high-speed low-power multipliers," *J. Eng. Sci. Technol. Rev.*, vol. 8, no. 2, pp. 1–7, 2015.

- 21. M. Lavanya and K. Saifuddin, "Implementation of Low Power 4 Bit Dadda Multiplier Using Dadda Algorithm and Optimized Full Adder," *International Journal for Research and Development in Science and Technology (IJRDST)*, vol. 4, no. 2, pp. 31–33, Feb. 2020.

- 22. P. Ancha and G. Hareesh, "Design of Approximate 4:2 Compressor for High-Speed Multiplication," *International Journal of Engineering Research & Technology (IJERT)*, vol. 10, no. 6, pp. 419–424, June 2021.

- 23. R. Padmanabhan et al., "Efficient Hybrid 3:2 Counter-Based Dadda Multiplier," Journal of Engineering, vol. 10, no. 5, pp. 123-130, May 2022.

- 24. Shabbir et al., "Low-Power and High-Speed VLSI Multiplier Using HA-CSLA and BEC Architecture," *International Journal of Engineering Research & Technology (IJERT)*, vol. 11, no. 6, pp. 419–424, June 2023.